Les disjoncteurs traditionnels ont leurs limites, mais les progrès ont conduit à des améliorations significatives.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat exclusif de contenu numérique avec Bodo’s Power Systems.

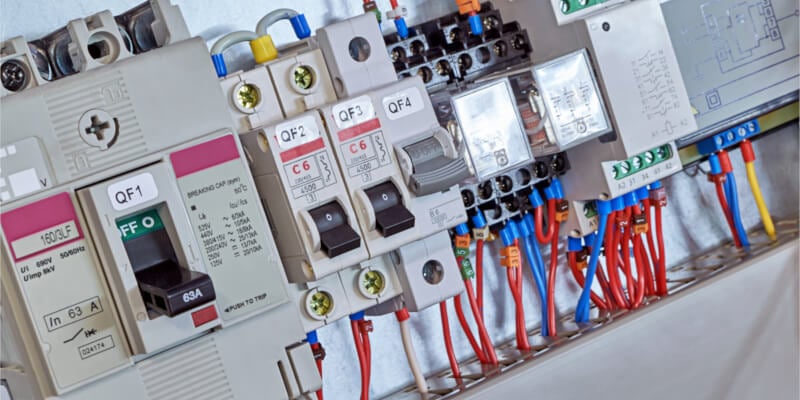

Le milieu du XXe siècle a vu des innovations significatives dans les systèmes électriques résidentiels et industriels. L’une des avancées les plus impactantes a été le passage des fusibles traditionnels remplaçables aux disjoncteurs miniatures (MCB). Bien que les fusibles aient fourni une protection de base, ils devaient être remplacés après avoir sauté. Les disjoncteurs, en revanche, pouvaient être facilement réinitialisés après avoir déclenché. Cette commodité a conduit les codes de construction et les normes électriques à favoriser les disjoncteurs par rapport aux fusibles dans les nouvelles constructions.

Image utilisée avec l’aimable autorisation de Adobe Stock

Tendances des disjoncteurs

Les innovations telles que les interrupteurs différentiels à courant de fuite (GFCI) et les interrupteurs différentiels d’arc (AFCI) ont encore amélioré les disjoncteurs au fil des ans. Malgré ces améliorations, les disjoncteurs traditionnels ont encore des limites en raison de leurs relais mécaniques. Ces limites comprennent :

- Arc électrique : Lorsque les contacts des relais s’ouvrent ou se ferment, un arc électrique peut se produire, ce qui est particulièrement problématique en cas de défaut de circuit avec des courants élevés.

- Vitesse de déconnexion : La vitesse à laquelle un disjoncteur électromécanique se déconnecte est limitée par la physique de sa bobine et la masse inerte du relais.

- Usure : Au fil du temps, les contacts d’un relais mécanique s’usent, limitant le nombre de cycles d’interruption.

La tendance actuelle est un nouveau type de disjoncteur qui remplace le relais électromécanique par des dispositifs électroniques de puissance, connus sous le nom de disjoncteurs à semi-conducteurs (SSCB) ou disjoncteurs à semi-conducteurs (SCB). Ces SSCB offrent plusieurs avantages :

- Arc électrique : Les interrupteurs à semi-conducteurs se connectent et se déconnectent sans produire d’arcs, éliminant le besoin de fonctions spéciales de suppression d’arc.

- Vitesse de déconnexion : Libérés des contraintes d’une bobine magnétique, les interrupteurs à semi-conducteurs peuvent fonctionner des centaines de fois plus rapidement que les relais électromécaniques. Cette réponse rapide permet d’interrompre le courant avant qu’il ne devienne dangereux, ce qui est crucial pour une protection efficace des circuits.

- Usure : Parce qu’ils n’ont pas de composants mécaniques, les interrupteurs à semi-conducteurs peuvent effectuer un nombre illimité de cycles de connexion/déconnexion sans dégradation.

Le passage de l’éclairage incandescent à l’éclairage LED offre une analogie utile pour la transition des disjoncteurs électromécaniques aux disjoncteurs à semi-conducteurs. L’adoption généralisée des ampoules LED qui pouvaient être installées dans des douilles existantes conçues pour des ampoules à incandescence a permis aux clients de faire la transition progressivement. Au début, lorsque l’éclairage LED avait une prime de prix élevée, les utilisateurs pouvaient installer des ampoules LED uniquement dans les douilles à usage intensif où les gains en efficacité justifiaient le coût supplémentaire.

Défis des disjoncteurs à semi-conducteurs

De même, le développement des SCB installés directement dans des panneaux électriques initialement conçus pour les disjoncteurs électromécaniques permettra une transition progressive et méthodique. Cependant, cela introduit des défis significatifs, le premier étant la gestion thermique. Les disjoncteurs traditionnels basés sur des relais mécaniques ont une très faible résistance de contact, produisant peu de chaleur en fonctionnement normal. Par conséquent, les panneaux de disjoncteurs ont des dispositions minimales pour l’élimination de la chaleur, avec une circulation d’air limitée et pas de dissipateurs thermiques. Compte tenu de ces contraintes, les SCB conçus pour les panneaux existants doivent générer un minimum de chaleur, nécessitant une faible résistance de commutation effective du dispositif à semi-conducteur.

Le deuxième défi pour les SCB est la taille. Pour être compatibles avec les panneaux existants, les SCB doivent se conformer au facteur de forme des disjoncteurs électromécaniques existants, ce qui limite le nombre de dispositifs pouvant être installés en parallèle pour atteindre la résistance cible définie par les contraintes thermiques du panneau de disjoncteurs. Ces contraintes rendent nécessaires des dispositifs avec une très faible valeur RDS(on) dans des boîtiers compacts.

Le SiC JFET de Qorvo répond à ces exigences strictes avec la plus faible résistance de commutation par surface (RDS·A) de tous les types de dispositifs dans sa gamme de tension, grâce à sa structure simple.

La figure 1(a) montre une section transversale simplifiée d’un SiC JFET de Qorvo avec une tension gate-source VGS = 0 et une tension drain-source VDS quasi nulle. Cela représente l’une des milliers de cellules parallèles dans une puce JFET avec des terminaux étiquetés Source, Gate et Drain. Le SiC JFET de Qorvo possède deux jonctions PN, donc deux diodes : drain-to-gate et gate-to-source, représentées dans la figure superposées sur les jonctions PN correspondantes. Dans cet état non polarisé, un canal très conducteur existe entre le Drain et la Source, permettant aux électrons de circuler librement dans les deux directions, offrant la faible résistance de commutation distinctive du SiC JFET de Qorvo.

Figure 1. Section transversale du JFET vertical (a) sans tensions de polarisation, et (b) tensions de polarisation pour la caractérisation de VG(th). Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Autour de chaque jonction PN se trouve une région de déplétion très résistive, car les porteurs mobiles ont été repoussés de la jonction PN. Les régions de déplétion drain-gate sont indiquées en gris dans la figure 1. Dans (b), l’application d’une tension drain-source suffisante motive le flux de courant. Cependant, le courant est presque nul, bloqué par l’expansion des régions de déplétion due à l’application d’une tension gate-source négative. Lorsque ces régions de déplétion se rencontrent, le canal est pincé.

Le SiC JFET de Qorvo est normalement allumé (entièrement conducteur) sans tension gate-source appliquée et nécessite une tension VGS négative pour être et rester éteint. Bien que certains relais à semi-conducteurs bénéficient de cet état normalement allumé, la plupart nécessitent un état par défaut normalement éteint. Le SiC JFET de Qorvo, normalement allumé, fonctionne bien pour les deux types, car l’ajout de quelques composants simples peut le maintenir dans un état normalement éteint, même sans alimentation de contrôle. Mais d’abord, quelques graphiques peuvent aider à comprendre la construction du SiC JFET de Qorvo.

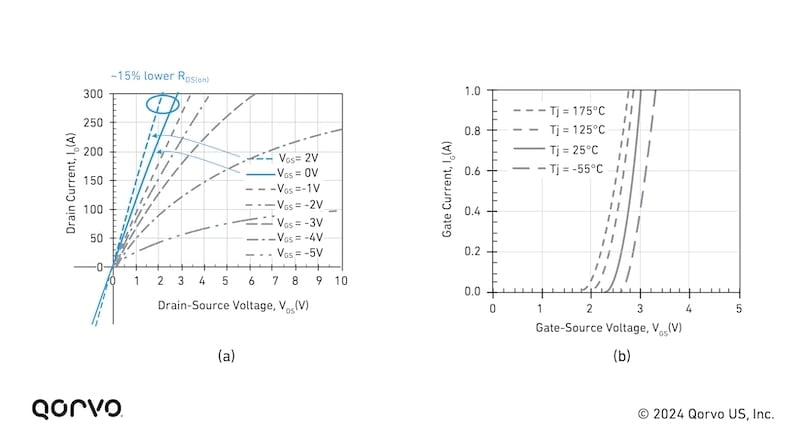

La figure 2(a) montre les caractéristiques de sortie avec diverses tensions gate-source à température ambiante d’un JFET SiC 750 V, 4,3 mΩ dans un boîtier TOLL (MO-229), numéro de pièce UJ4N075004L8S. La pièce typique a une tension de seuil gate VG(th) = -6V.

Avec VGS = -5V, la largeur du canal est fortement rétrécie par les régions de déplétion, de sorte que le flux de courant est limité. Le courant augmente légèrement avec VDS, et le JFET est en « saturation ». À VGS = -4V, les régions de déplétion sont plus étroites, rendant le canal plus large et augmentant ainsi la conductivité (réduisant la résistance de commutation). Cette courbe montre l’effet de l’augmentation de VDS et du rétrécissement des régions de déplétion, déformant la courbe caractéristique de sortie jusqu’à ce qu’il y ait peu d’augmentation du courant par rapport à VDS. D’autre part, l’augmentation de VGS diminue la largeur des régions de déplétion, ce qui élargit le canal et augmente la conductivité. La figure montre des courbes correspondant à certaines valeurs de VGS jusqu’à +2V, qui est la dernière tension de test VGS.

Figure 2. UJ4N075004L8S (a) caractéristiques de sortie à 25°C, et (b) courant de gate par rapport à VGS. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Notez que dans ces figures, RDS(on) est la résistance de commutation caractérisée soit à VGS = 0V soit à VGS = +2V. Une légère tension positive VGS, comme de 2 à 2,5 V, réduit encore les régions de déplétion drain-gate et réduit RDS(on) de 15 %, en fonction des conditions de fonctionnement. Communément appelé surmenage, c’est un moyen facile de minimiser RDS(on) du JFET sans risque de dommage ou de dérive des paramètres – encore un avantage du SiC JFET de Qorvo dans les applications nécessitant un fonctionnement à froid et une longue durée de vie.

Le coefficient de température de la résistance de commutation (CT) est positif, ce qui, combiné à la vitesse de commutation contrôlable via le pilote de gate, rend le parallélisme facile. Cependant, le fort CT doit être pris en compte lors de la sélection des pièces et de la décision du nombre à mettre en parallèle. Même à des températures de fonctionnement élevées, le SiC JFET de Qorvo présente une perte de conduction par taille de boîtier nettement inférieure par rapport aux technologies de dispositifs concurrentes.

La figure 2(b) montre le courant de gate par rapport à VGS pour le UJ4N075004L8S de Qorvo, où la diode gate-source du JFET SiC est polarisée en passant. La tension de genou de la diode dépendante de la température est clairement visible, et la pente correspond à la résistance de gate du JFET, qui est de 0,4 Ω. VGS est dans une plage de 2 à 2,6 V avec IG dans la plage des milliampères et la température s’étendant de -55 à 175°C. Ce graphique montre également le coefficient de température de la tension directe de la diode gate-source du JFET de -3,2 mV/°C, qui peut être utilisé pour mesurer la température de la puce du JFET avec un simple circuit amplificateur différentiel.

La structure simple du SiC JFET de Qorvo offre une conductivité inégalée, mais cette simplicité procure également une fiabilité et une durabilité incomparables. Le courant passe directement à travers le matériau SiC dopé avec des électrons extrêmement mobiles. Il n’y a aucune jonction PN dans le chemin du courant, ni de courant de surface. Cette conception garantit aucun mécanisme de dégradation, aucune hystérésis ou effet dynamique inhabituel. De plus, un test de vieillissement n’est pas nécessaire. Tant que les conditions de fonctionnement sûres ne sont pas largement dépassées, le fonctionnement du SiC JFET de Qorvo reste constant même après de nombreuses années.

Un autre trait final résulte de la simplicité de la structure du SiC JFET de Qorvo : la robustesse. Le matériau SiC peut supporter des températures internes élevées, de centaines de degrés Celsius, sans changement de paramètres, à condition que l’énergie reste dans des limites sûres. Cela permet au SiC JFET de Qorvo de couper des courants très élevés, y compris des courts-circuits, pour un nombre quelconque de cycles. Les disjoncteurs et relais électromécaniques endurent un nombre limité de cycles de commutation d’urgence, parfois un seul.

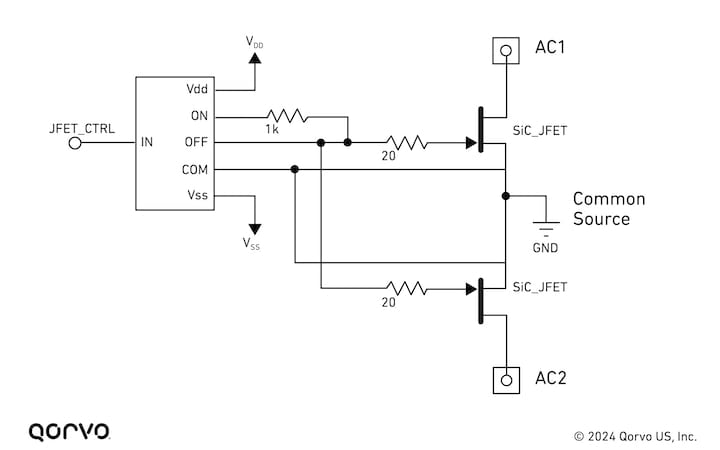

La figure 3 présente une configuration de blocage bidirectionnel avec un simple surmenage des JFET. Ce circuit est normalement allumé, ce qui signifie que les JFET sont en marche lorsqu’il n’y a pas d’alimentation de gate. Un pilote de gate disponible dans le commerce conduit directement chaque gate de JFET sans besoin de régulation de tension. La valeur de la résistance en état de marche dépend du courant de gate JFET souhaité ; au moins 1 mA est suffisant pour surmener le gate du JFET, tandis que 5 mA ou plus sont recommandés pour un contrôle facile de la température sur la puce. Notez que la vitesse de mise en marche est relativement lente avec la grande résistance de gate en état de marche, mais cela est souhaitable pour de nombreuses applications SCB et de relais.

Figure 3. Circuit à commande directe avec blocage bidirectionnel et état normalement allumé. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

La tension d’alimentation négative du pilote de gate JFET peut aller de -30 V minimum à un maximum recommandé de -12 V pour VSS ou un maximum absolu de 2 V en dessous de la valeur minimale de tension seuil du SiC JFET spécifiée dans la fiche technique. La tension d’alimentation positive dépend de la valeur de verrouillage en sous-tension (UVLO) du pilote de gate sélectionné. Par exemple, un pilote de gate comme le UCC5304 peut avoir aussi peu que 6 V pour VDD, permettant ainsi d’ajuster la résistance de gate en état de marche en conséquence.

La figure 4 montre une configuration de blocage bidirectionnel, à nouveau avec un simple surmenage des JFET. Un état normalement éteint est obtenu en connectant un MOSFET silicium basse tension en série avec chaque JFET dans une configuration quasi-cascode. Un pilote de gate disponible dans le commerce conduit directement chaque gate de JFET, tandis qu’un superviseur de tension contrôle chaque MOSFET, s’assurant qu’ils restent allumés lorsque la tension d’alimentation du pilote de gate est dans la plage de fonctionnement. Le superviseur de tension dans le schéma bloc surveille la tension de commande gate négative, de sorte que le MOSFET reste éteint jusqu’à ce que le JFET puisse être fiablement éteint par le pilote de gate JFET. Alternativement, le superviseur de tension pourrait être remplacé par un pilote de gate.