Cet article examine les différences entre le carbure de silicium et le silicium, ainsi que la manière dont des techniques de circuit comme la commutation douce peuvent être optimisées au-delà de ce qui est possible avec le silicium.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat de contenu numérique exclusif avec Bodo’s Power Systems.

Sur le papier, la technologie du carbure de silicium (SiC) présente des avantages par rapport au silicium (Si) qui la rendent apparemment adaptée pour remplacer directement les MOSFET existants en électronique de puissance. Cela est vrai dans une certaine mesure, mais il est possible de tirer beaucoup plus de SiC en prêtant attention à la manière dont la technologie diffère du silicium et comment les techniques de circuit, telles que la commutation douce, peuvent être optimisées au-delà de ce qui est pratique avec le silicium.

Le bandgap plus large du SiC par rapport au silicium se traduit par une tension de claquage et une mobilité des électrons plus élevées, ce qui réduit ensemble la résistance en état passant. Cela permet également des vitesses de commutation plus rapides comparées au silicium, ce qui entraîne une amélioration de l’efficacité et la possibilité de concevoir des systèmes d’électronique de puissance avec des formats plus petits. Le SiC a également une conductivité thermique sensiblement plus élevée que celle du silicium, ce qui permet de concevoir des dispositifs d’électronique de puissance qui peuvent fonctionner à des températures plus élevées sans sacrifier la performance ou la fiabilité.

Image utilisée avec l’aimable autorisation de Adobe Stock

Alors que les circuits basés sur des MOSFETs à superjonction conventionnels en silicium doivent seulement tenir compte des techniques simples de commutation douce, la fréquence typique plus élevée de fonctionnement signifie que le SiC bénéficie d’une analyse minutieuse de l’endroit et du moment où les pertes se produisent. Cette analyse peut, à son tour, mener à des solutions novatrices qui évitent les pertes inhérentes aux conceptions de circuits basés sur des MOSFETs conventionnels.

Par exemple, un avantage clé de la technologie à large bandgap comme le SiC est la capacité de garantir une tension de claquage plus élevée pour une résistance à l’état passant donnée. Cela permet l’utilisation d’une couche de dérive plus fine qui présente moins de résistance par rapport aux couches plus épaisses nécessaires pour les dispositifs en silicium micronique. En même temps, la composition du réseau cristallin offre une mobilité des porteurs plus élevée. Le résultat net est une conductivité considérablement plus élevée.

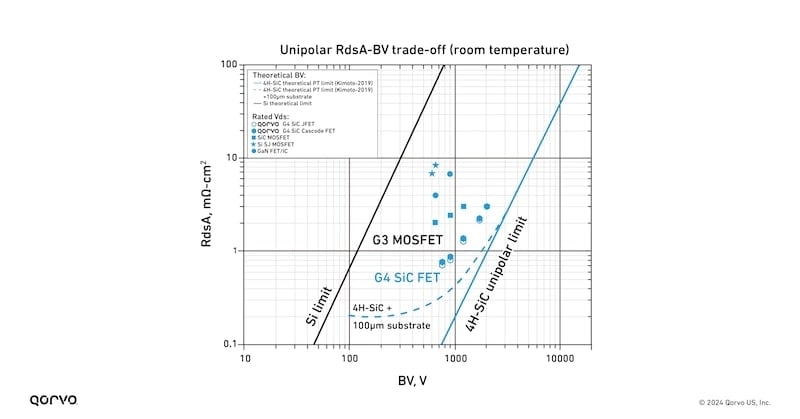

Le transistor à effet de champ à jonction (JFET) est la meilleure option pour minimiser la résistance drain-source. Dans un MOSFET, les porteurs doivent traverser la surface de la région de base P (puits P) à travers un canal d’inversion résistif à l’interface MOS avant d’entrer dans la région de dérive de type N. Cependant, dans un JFET, il n’y a pas de canal d’inversion. En utilisant une haute mobilité des porteurs majoritaires en volume, le JFET approche la limite théorique de la résistance à l’état passant par rapport à la tension de claquage. Les dispositifs à base de JFET en SiC de Qorvo permettent une conception de transistor avec une marge de sécurité plus grande sur la tension de claquage par rapport aux conceptions à base de MOSFET et une résistance à l’état passant presque moitié moins élevée que celle des pièces concurrentes.

Figure 1. Les FETs SiC de quatrième génération de Qorvo montrent une RdsA d’environ la moitié de celle des MOSFETs SiC traditionnels. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Conventuellement, l’utilisation d’un JFET en mode appauvrissement seul introduit des défis de conception de circuit. En tant que dispositif normalement activé, il a besoin d’une tension négative pour s’éteindre complètement. Toutefois, les MOSFETs en SiC ont des tensions seuils faibles, donc les tensions négatives de grille ne sont pas rares dans les circuits réels. L’application de tensions négatives empêche l’activation accidentelle des transistors aux températures extrêmes où la tension de seuil peut tomber en dessous des niveaux nominaux.

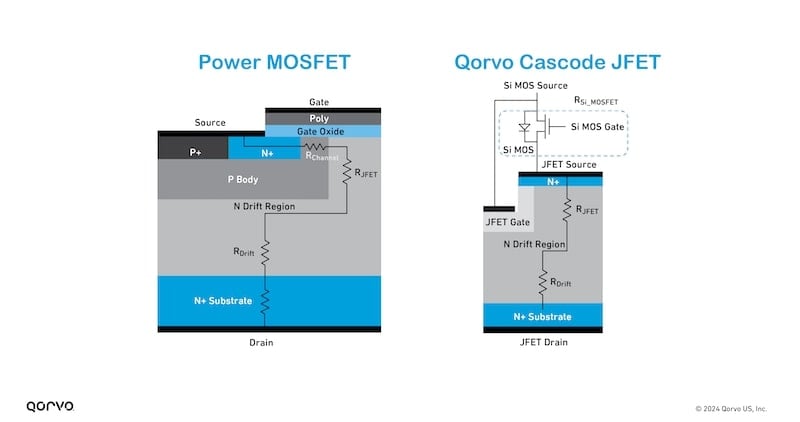

La solution de Qorvo combine un JFET en SiC avec un MOSFET en silicium de basse tension dans une structure en cascode où la tension grille-source du JFET en SiC est l’inverse de la tension drain-source du MOSFET en Si. Cette structure en cascode est illustrée dans la Figure 2. Dans la configuration en cascode, la commande de grille externe contrôle une tension drain-source de MOSFET en Si de basse tension, ce qui commande indirectement le JFET en SiC de haute tension. Cette configuration en cascode fournit un contrôle familier aux ingénieurs habitués à travailler avec des MOSFETs à superjonction en silicium. La basse tension de fonctionnement du MOSFET contribue à moins de 10 % à la résistance totale à l’état passant de la paire de dispositifs. Pour faciliter l’intégration, Qorvo fournit cette configuration dans un seul boîtier.

Les structures en cascode offrent un contrôle de la commutation grâce au MOSFET en Si de basse tension, découplant la logique de contrôle du JFET de haute tension. Ce découplage offre l’opportunité d’optimiser la plage de tension de contrôle de la grille et la charge de la grille pour le MOSFET en Si de basse tension sans sacrifier les avantages de performance complets du JFET en SiC. Contrairement aux MOSFETs en SiC conventionnels qui nécessitent généralement une tension de grille aussi élevée que 18 V pour activer complètement le dispositif et obtenir tous les avantages d’une faible résistance à l’état passant, l’architecture en cascode permet des tensions de contrôle de grille maximales plus faibles et élimine la nécessité de tensions négatives à l’état éteint. Cette réduction de la plage de tension réduit la charge de la grille de 50 % (de 18 V/-4 V à 10 V/0 V), réduisant potentiellement les pertes pendant la commutation, en particulier pour les applications de commutation douce à faible charge.

Passer au SiC avec une structure JFET réduit de manière significative la taille de la puce. Le dispositif de Qorvo a une réduction presque dix fois de la surface de la puce avec la même capacité de gestion de puissance que les dispositifs en silicium à superjonction. La conductivité thermique du SiC et son efficacité supérieure compensent l’augmentation de la résistance thermique qui accompagne une puce sensiblement plus petite. Toute augmentation supplémentaire de la résistance thermique est compensée par l’utilisation du frittage de l’argent pour la fixation de la puce, ce qui améliore la conductivité thermique six fois par rapport aux soudures conventionnelles.

L’application d’une structure en cascode à un JFET en SiC améliore encore l’efficacité en réduisant les capacités parasites qui affectent les dispositifs à superjonction en silicium et les MOSFETs en SiC. Les capacités parasites plus faibles améliorent également la densité en augmentant la fréquence de commutation au-delà de ce qui est pratique avec les dispositifs en silicium et même avec les MOSFETs en SiC.

Les avantages sont les plus apparents dans les architectures de circuits de commutation douce. Alors que les techniques de commutation douce utilisées avec les dispositifs en silicium abordent certaines des sources de perte les plus évidentes dues aux phases de mise en marche et d’arrêt du cycle de commutation, la capacité de commutation rapide de la dernière génération de transistors en SiC aborde des problèmes plus subtils qui sont généralement ignorés.

Figure 2. Vue en coupe latérale d’un MOSFET plan en SiC (à gauche) et d’un FET en SiC en cascode de Qorvo (à droite). La résistance du canal dominante (Rchannel) du MOSFET en SiC est remplacée par une résistance RDS(on) bien plus faible d’un MOSFET en Si basse tension dans une structure en cascode. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

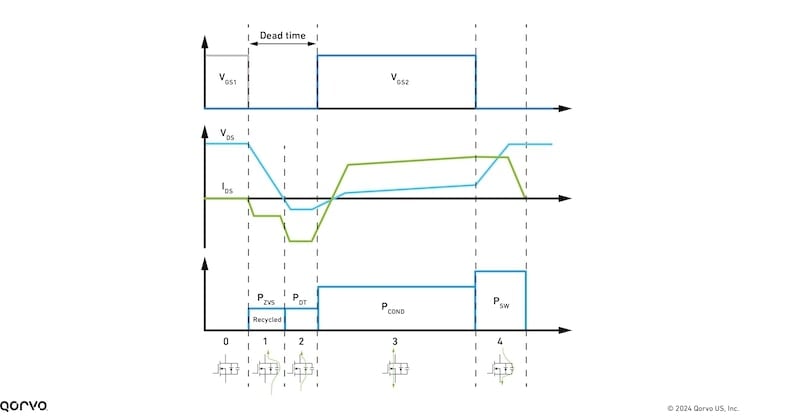

De nombreux circuits basés sur des dispositifs en silicium emploient la commutation à zéro tension (ZVS). Son but principal est de réduire la tension entre le drain et la source pendant la transition de mise en marche du transistor avant que le courant ne commence à circuler librement à travers le canal du transistor. Idéalement, le courant drain-source du dispositif (IDS) et la tension drain-source (VDS) ont presque zéro chevauchement, éliminant ainsi la perte de commutation à la mise en marche. La capacité de sortie (c’est-à-dire la somme des capacités drain-source et de la capacité entre la grille et le drain) est normalement entièrement chargée à la tension du bus de liaison DC pendant l’arrêt du dispositif lors du cycle précédent et est recyclée dans la charge pour éviter les pertes lors du prochain événement de mise en marche ZVS.

La mise en marche ZVS avec un dispositif en Si conventionnel peut entraîner une période de temps mort dans le cycle de commutation qui peut durer jusqu’à 300 ns en raison de la haute capacité de sortie des dispositifs en silicium. À une fréquence de commutation de 500 kHz (2 µs de période), un temps mort de 300 ns pendant les transitions de mise en marche et d’arrêt représente 30 % du cycle de travail. Le JFET en SiC offre un avantage clé par rapport aux MOSFETs en Si car il a une capacité de sortie 10 fois plus faible qui prend moins de temps à se libérer, en particulier à une faible tension de polarisation drain-source où la capacité de sortie augmente significativement pour les MOSFETs en Si. Les dispositifs à superjonction en silicium présentent une forte non-linéarité dans la courbe CV à faible polarisation drain-source, ce qui entraîne une durée de transition de tension élevée près de la tension du bus et de 0 V pendant la transition de commutation dans une topologie demi-pont. Cela réduit la durée du temps mort nécessaire pour la ZVS, ce qui peut être échangé contre un fonctionnement à plus haute fréquence ou plus de puissance délivrée à la charge.

Figure 3. Illustration des formes d’onde clés et de la répartition des pertes dans les applications de commutation douce ZVS. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

En raison du long temps de transition de tension et de la perte de commutation relativement élevée à l’arrêt, les conceptions de circuits ZVS utilisant des dispositifs en Si sont limitées à des fréquences de commutation inférieures à 150 kHz. Avec la capacité de commutation rapide du FET en SiC de Qorvo, la limite de fréquence de commutation est poussée au-delà de 500 kHz. Comme pour les pertes de commutation à la mise en marche, l’efficacité s’améliore si le chevauchement entre la chute de courant et l’augmentation de la tension drain-source lors de l’arrêt est minimisé.

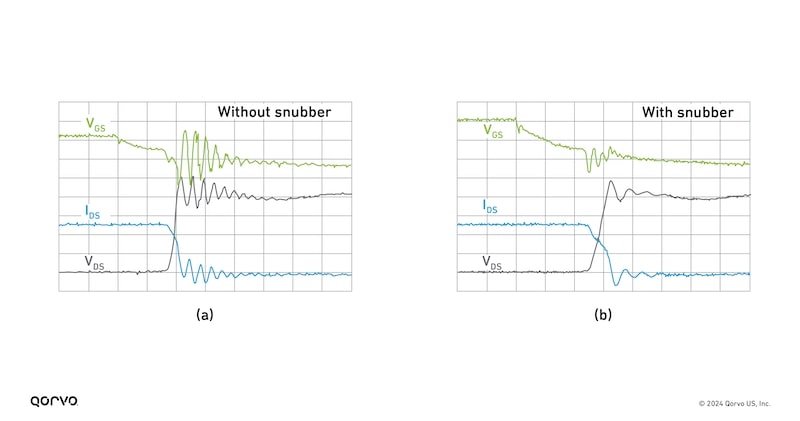

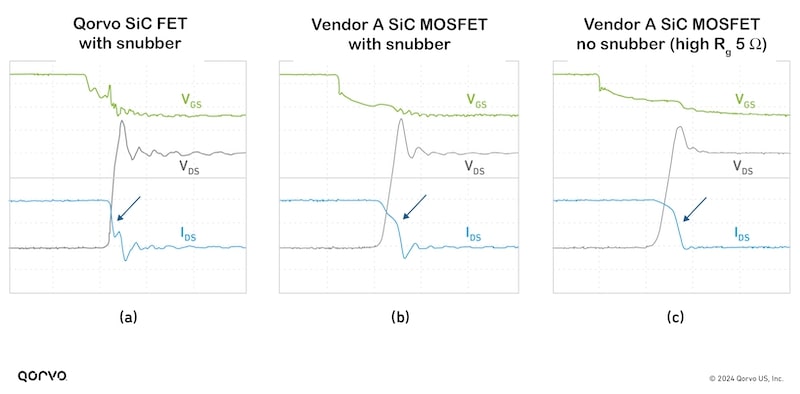

Toutefois, les interférences électromagnétiques deviennent plus difficiles à gérer avec l’augmentation de la vitesse de commutation. Les concepteurs doivent minimiser avec diligence les parasites de la carte PCB provenant des boucles de commutation de courant critiques dès les premières phases de la conception pour tirer pleinement parti de la capacité de commutation rapide du SiC. Cependant, il y a une limite à l’optimisation possible lorsque les exigences de sécurité (par exemple, la distance d’isolement, la distance de fuite, etc.) sont prises en compte. Une fois la conception du circuit finalisée, il existe deux moyens populaires pour affiner davantage les pics de tension drain-source à l’arrêt et les oscillations. L’un consiste à utiliser une haute résistance de grille (Rg) pour ralentir la vitesse de commutation du dispositif. Un moyen plus efficace et plus efficient est d’utiliser un circuit d’amortissement (snubber), comme illustré dans la Figure 4, avec une faible résistance de grille. En d’autres termes, utilisez une petite résistance de grille pour permettre une commutation rapide des dispositifs en SiC, et utilisez un RC d’amortissement pour contrôler les pics et les oscillations de VDS. Le condensateur d’amortissement du dispositif (Cs) assure le contrôle du dépassement des pics de VDS tandis que le condensateur (Cd) minimise les inductances parasites de la boucle d’alimentation en étant placé près du demi-pont de commutation rapide. Les résistances (Rs et Rd) assurent l’amortissement des oscillations de VDS.

Figure 4. Schéma DPT avec un circuit RC d’amortissement sur les deux interrupteurs pour (a) la commutation dure et (b) la commutation douce ZVS. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Une idée fausse courante est que l’utilisation d’un circuit d’amortissement est inefficace. Pour une topologie de demi-pont—typiquement utilisée dans les applications ZVS telles que LLC ou PSFB—l’utilisation d’un circuit d’amortissement est bien plus efficace que l’utilisation d’une haute résistance de grille car le condensateur drain-source ajouté ne génère aucune perte de mise en marche. Pendant la phase dv/dt de l’arrêt, le courant de déplacement du dispositif de roue libre diminue encore le courant d’arrêt du dispositif qui a été activement éteint, réduisant ainsi le chevauchement tension-courant pour réduire considérablement la perte d’arrêt (Eoff). Le niveau de courant de déplacement est déterminé par l’équation I = C*dv/dt. C est la capacité de sortie équivalente qui inclut à la fois la capacité de sortie du dispositif (Coss) et la capacité de l’amortissement supplémentaire Cs connectée en parallèle entre le drain et la source du dispositif. Avec une capacité supplémentaire d’amortissement entre le drain et la source et un dv/dt élevé (c’est-à-dire une faible résistance de grille), le courant de déplacement sera plus élevé. Cela laisse moins de courant à chevaucher avec VDS pour le dispositif d’arrêt actif, réduisant ainsi la perte de commutation à l’arrêt. Cette approche permet de contenir les oscillations et les pics de VDS sans sacrifier autant la vitesse de commutation du dispositif que si on avait utilisé une solution Rg élevée. La Figure 5 montre des formes d’onde de test de double impulsion à l’arrêt, avec et sans circuit d’amortissement, pour démontrer intuitivement qu’utiliser un circuit d’amortissement avec une faible résistance de grille réduit considérablement le chevauchement tension-courant, ce qui réduit à son tour la perte de commutation à l’arrêt.