La réduction des pertes de commutation des MOSFET SiC est possible, mais des défis se posent pour atteindre des vitesses de commutation élevées lors du fonctionnement des modules de puissance.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat de contenu numérique exclusif avec Bodo’s Power Systems.

Le passage des modules de puissance basés sur la technologie IGBT Si aux modules de puissance basés sur la technologie MOSFET SiC est inévitable. Cependant, les préférences de facteur de forme, héritées de l’ère des IGBT Si, continuent de freiner la commercialisation de la technologie SiC en raison de leur forte inductance parasite. Mitsubishi Electric a développé un boîtier NX modifié avec une structure interne de barre omnibus adaptée aux MOSFETs SiC.

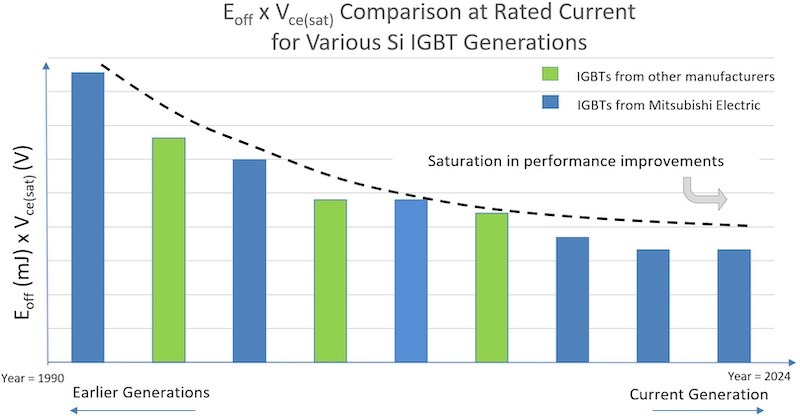

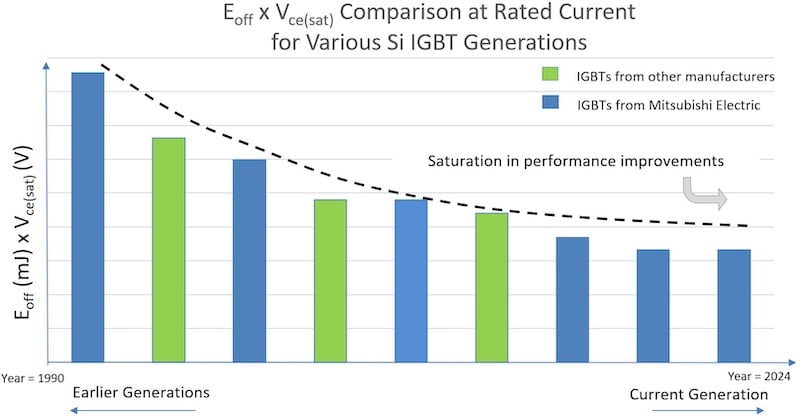

La technologie des puces IGBT Si a évolué et les améliorations apportées d’une génération de puces à la suivante sont de plus en plus étroites (voir Figure 1), ce qui indique que chaque nouvelle génération se rapproche des limites physiques du matériau lui-même.

Les semi-conducteurs à large bande interdite tels que les MOSFETs SiC offrent la possibilité de réduire de manière significative les pertes de puissance globales du semi-conducteur. Un aspect de la réduction potentielle des pertes en utilisant des MOSFETs SiC provient de la possibilité de réduire les pertes de commutation, d’augmenter la fréquence de commutation. En conséquence, les composants du filtre peuvent être optimisés, et les pertes correspondantes diminueraient, ce qui entraînerait une réduction globale des pertes du système.

Figure 1. Comparaison entre Eoff et VCE(sat) pour différentes générations d’IGBT Si. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Défi : Considérations sur l’emballage des MOSFETs SiC

La réduction des pertes de commutation avec les MOSFETs SiC est possible car ils peuvent commuter beaucoup plus rapidement que les IGBTs Si. Cependant, certains défis se posent pour atteindre des vitesses de commutation élevées pendant le fonctionnement du module de puissance.

Surtension de commutation : La surtension de tension inductive lors de la désactivation du MOSFET (∆VDS) est une fonction de l’inductance parasite (LS) de l’emballage du module de puissance et du taux de variation du courant de drain (\(\frac{dI_{D}}{dt}.\))

\[\Delta V_{DS}=-L_{S}\times\frac{dI_{D}}{dt}\]

Figure 2. Pic de VDS par rapport à \(\frac{dI_{D}}{dt}\). Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Figure 3. Schéma interne du module NX (à gauche), forme d’onde du courant d’activation pour le module NX standard (à droite). Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Il est possible de déduire de la Figure 2 que plus l’inductance interne de l’emballage est élevée, plus la variation de courant de drain admissible maximale (\(\frac{dI_{D}}{dt}.\)) est faible.

Équilibrage interne du courant : La capacité nominale d’un module de puissance dépend du nombre de puces individuelles qui peuvent être connectées en parallèle à l’intérieur de l’emballage. Maintenir une répartition homogène du courant de drain entre les puces est important pendant les opérations statiques et dynamiques. Par conséquent, l’emballage du module de puissance doit être conçu pour assurer un équilibrage adéquat du courant des puces individuelles.

Préférence et défis de facteur de forme : Les modules demi-pont IGBT Si appartenant à des classes de 650 V, 1200 V ou 1700 V avec un courant nominal dans la plage de plusieurs centaines d’ampères sont largement disponibles dans le boîtier NX, qui s’est établi dans le segment de conversion de puissance industrielle depuis plusieurs années. Idéalement, il serait avantageux de conserver le facteur de forme du module de puissance existant (comme le boîtier NX établi). Cependant, le boîtier NX classique a une inductance interne (LS) d’environ 20 nH, ce qui le rend inadapté à l’adoption du SiC. De plus, comme le montre la représentation de la Figure 3, le boîtier NX classique nécessite que les puces IGBT Si soient placées le long de l’axe long du module de puissance. En conséquence, le partage dynamique du courant entre les puces n’est pas optimal et pose un défi pour l’adoption directe du SiC.

Boîtier NX à faible inductance pour l’adoption du SiC

La disposition interne du boîtier NX a été modifiée pour l’adoption du SiC. La Figure 4 montre la section transversale interne du boîtier NX modifié.

Figure 4. Section transversale interne du boîtier NX modifié pour l’adoption du SiC. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Les barres omnibus CC+ et CC- sont disposées dans une « structure stratifiée » placée aussi près l’une de l’autre que possible (séparées par une couche d’isolation) pour maximiser la compensation du champ magnétique. De plus, les barres omnibus CC+ et CC- sont directement reliées au substrat, évitant ainsi une inductance parasite supplémentaire due aux connexions de fils de liaison aux bornes. De plus, les puces ne sont pas placées le long de l’axe long du module (comme c’était le cas avec la conception NX classique utilisant des IGBTs Si). Un schéma de circuit optimisé a été développé (Figure 5) pour obtenir un partage de courant optimal entre les différentes puces. L’inductance interne du module NX à faible inductance modifié a été mesurée à 9 nH. Cela correspond à une réduction de l’inductance parasite d’environ 47% par rapport au module de puissance NX classique.

Figure 5. Agencement interne du boîtier NX modifié (à gauche), forme d’onde du courant d’activation pour le boîtier NX modifié (à droite). Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Le module SiC NX a été lancé avec une capacité nominale de 1700 V/600 A (FMF600DXE-34BN) et une capacité nominale de 1200 V/600 A (FMF600DXE-24BN). Les deux dispositifs ont une topologie demi-pont (configuration 2 en 1). Le module de puissance comprend un socle en céramique (substrat AlN) et utilise une encapsulation en gel de silice. Les modules de puissance sont basés sur la technologie de puce SiC de 2ème génération de Mitsubishi.

Figure 6. Photo du module SiC NX. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Comparaison des performances

Pour comprendre l’amélioration des performances à l’aide du module NX SiC modifié, une comparaison peut être effectuée en tenant compte des éléments suivants :

- Impact du boîtier NX modifié (par rapport au boîtier NX classique)

- Comparaison des performances de la puce MOSFET SiC elle-même (par rapport à la technologie IGBT Si)

L’élément 1 peut être analysé à l’aide de la relation de compromis présentée dans la Figure 7 – la surtension de tension inductive (VDS [V] pour les MOSFETs SiC et VCE [V] pour les IGBTs) et l’énergie de commutation à la désactivation (Eoff [mJ/Pulse]). Les conclusions suivantes peuvent être tirées de la Figure 7 en tenant compte des conditions de fonctionnement DC-Link = 1000V, IC (ou ID) = 600A et Tvj = 150°C :

a) Boîtier NX classique : La courbe rouge indique VCE [V] pour le 7ème IGBT Si de 1700 V et le MOSFET SiC de 2ème génération de 1700 V, en tenant compte du boîtier NX classique (LS = ~ 20nH). Il est possible d’obtenir des pertes de désactivation plus faibles (Eoff) avec le MOSFET SiC dans le même boîtier (classique), cependant, la surtension de tension inductive ne peut pas être maintenue dans la zone d’utilisation sûre en polarisation inverse avec une marge de sécurité adéquate.

b) Boîtier NX à faible inductance modifié : La courbe bleue indique VDS pour le MOSFET SiC de 1700 V en tenant compte du boîtier NX à faible inductance modifié. On peut voir que la zone d’utilisation sûre en polarisation inverse peut être maintenue sans compromettre l’Eoff. Étant donné que LS = 9nH, une résistance de gâchette de plus faible désactivation peut être sélectionnée.