La technologie SiC est cruciale pour favoriser la transition vers la mobilité électrique et améliorer l’efficacité des systèmes d’énergie renouvelable. Malgré des améliorations significatives dans la qualité et la disponibilité du matériau 4H-SiC, le défi de produire des tranches de SiC à faible densité de défauts et à haute performance pour des rendements optimaux persiste encore.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat de contenu numérique exclusif avec Bodo’s Power Systems.

Depuis l’introduction des premières tranches commerciales de SiC monocristallin au début des années 1990, aucune modification n’a été apportée à leur composition, seulement à leur diamètre et à la réduction de leurs défauts au fil du temps. SmartSiC est un substrat ingénieux basé sur un nouveau paradigme, combinant sur un seul substrat une couche supérieure de haute qualité en SiC monocristallin liée à une tranche de SiC polycristallin hautement conducteur électriquement pour permettre des gains sans précédent en termes de performance et de fiabilité des dispositifs.

La technologie du carbure de silicium (SiC) dans l’électronique de puissance est cruciale pour favoriser la transition vers la mobilité électrique et améliorer l’efficacité des systèmes d’énergie renouvelable. Avec la demande croissante sur le marché, les entreprises de semiconducteurs de puissance sont sous pression pour augmenter rapidement leur capacité de production. Malgré des améliorations significatives dans la qualité et la disponibilité du matériau 4H-SiC, le défi de produire des tranches de SiC à faible densité de défauts et à haute performance pour des rendements optimaux persiste encore.

En réponse à ce besoin pressant, un substrat ingénieux en SiC a été introduit pour répondre aux exigences de l’industrie. Le lancement d’une ligne de fabrication dédiée en septembre 2023 marque une étape importante, signalant le début de la production à grande échelle de ce substrat innovant. Cette initiative stratégique est prête à révolutionner le paysage de la technologie SiC, en offrant une solution révolutionnaire aux contraintes actuelles de fabrication et en ouvrant la voie à une efficacité et une performance accrues dans les applications d’électronique de puissance.

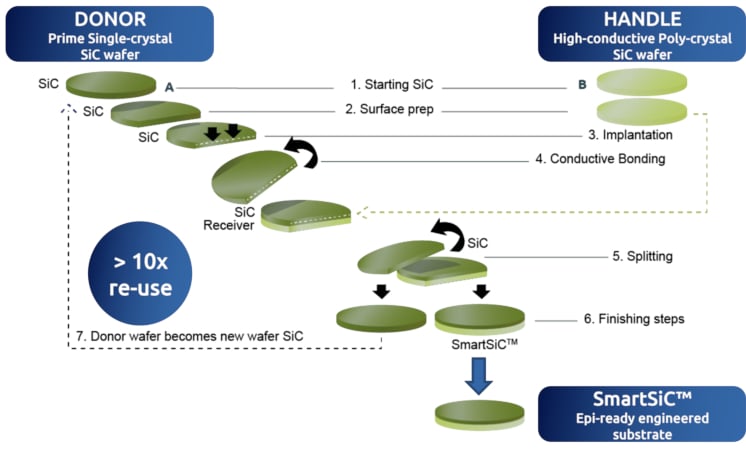

La fabrication des substrats SmartSiC repose sur la technologie Smart Cut et offre des avantages significatifs dans la fabrication des dispositifs en SiC. Voici un aperçu de ses caractéristiques et avantages clés :

- Couche supérieure de SiC de haute qualité : La technologie Smart Cut facilite le transfert d’une couche de SiC de haute qualité sur une tranche de support, servant de graine pour l’épithaxie de dérive à croître. Ce processus est crucial pour optimiser le rendement et la fiabilité des dispositifs, assurant que les dispositifs résultants répondent à des normes de qualité strictes.

- Tranche de support à faible résistivité : La technologie incorpore une tranche de support à faible résistivité avec une résistivité typique de 2 mOhm.cm (la résistivité standard du matériau SiC étant d’environ 20 mOhm.cm). Cette fonctionnalité améliore la conduction des dispositifs tout en permettant de minimiser les pertes de commutation, améliorant finalement la performance globale des applications basées sur des dispositifs en SiC.

- Compatibilité avec différents diamètres de tranches : La technologie Smart Cut est compatible avec tout diamètre de substrat et est utilisée pour des tranches de 150 mm et 200 mm.

Basé sur les caractéristiques décrites ci-dessus, le substrat SmartSiC obtenu consiste en une couche supérieure monocristalline 4H-SiC de haute qualité et d’épaisseur submicronique (entre 400 et 800 nm) liée à une tranche de support en SiC polycristallin. Le substrat final a une épaisseur de 350 µm pour des tranches de 150 mm et de 500 µm pour des tranches de 200 mm. Cette composition assure l’intégrité structurelle et la performance du substrat, contribuant à la fiabilité et à l’efficacité des dispositifs en SiC.

De plus, en permettant la réutilisation des tranches de donneurs monocristallins initiales grâce à la faible épaisseur de la couche supérieure monocristalline, la technologie SmartSiC offre l’utilisation la plus efficace des boules de SiC difficiles à obtenir. Comparée au traitement conventionnel des tranches de SiC, qui permet généralement l’extraction d’un maximum de 50 tranches par boule, la technologie Smart Cut permet la préparation de jusqu’à 500 substrats ingénieux à partir de la même boule. Cette augmentation substantielle de productivité représente une solution significative en termes de coûts et d’efficacité des ressources pour la fabrication de dispositifs en SiC.

Le processus Smart Cut appliqué à la fabrication des substrats SmartSiC est illustré dans la Figure 1.

Figure 1. Technologie Smart Cut adaptée au carbure de silicium. Image utilisée avec la permission de Bodo’s Power Systems [PDF]

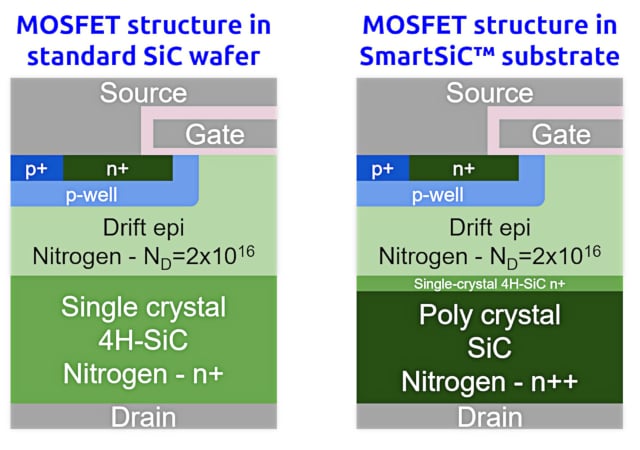

Pour étudier les avantages des substrats SmartSiC par rapport aux tranches standard de 4H-SiC monocristallin, des MOSFETs SiC planaires de type n, 13 mOhm/650 V Gen2 ont été fabriqués sur les deux types de substrats et traités simultanément comme un seul lot.

La tranche de 4H-SiC monocristallin, considérée comme référence, est dopée à l’azote avec une résistivité typique de 20 mOhm.cm, tandis que la tranche de support en poly-SiC du substrat SmartSiC a un dopage en azote plus élevé et une résistivité typique de 2 mOhm.cm. L’épithaxie de dérive est dopée à l’azote, avec une concentration en dopage ND ≈ 2×1016 cm-3. Des implantations de phosphore et d’aluminium ont été utilisées pour former, respectivement, les régions de source et de corps. L’oxyde de grille avait une épaisseur de 55 nm et était constitué de SiO2, tandis que du poly-Si de type n fortement dopé était utilisé comme électrode de grille. Les structures du MOSFET de véhicule test sur la tranche de SiC monocristallin standard et sur le substrat SmartSiC™ sont illustrées dans la Figure 2.

Résultats

Les résultats obtenus sur les MOSFETs planaires SiC de 13 mOhm 650 V Gen2 sont présentés ici.

Figure 2. Structure du MOSFET planaire SiC Gen 2 utilisé comme véhicule test, implémenté sur une tranche de 4H-SiC monocristallin (à gauche) et sur un substrat SmartSiC (à droite). Image utilisée avec la permission de Bodo’s Power Systems [PDF]

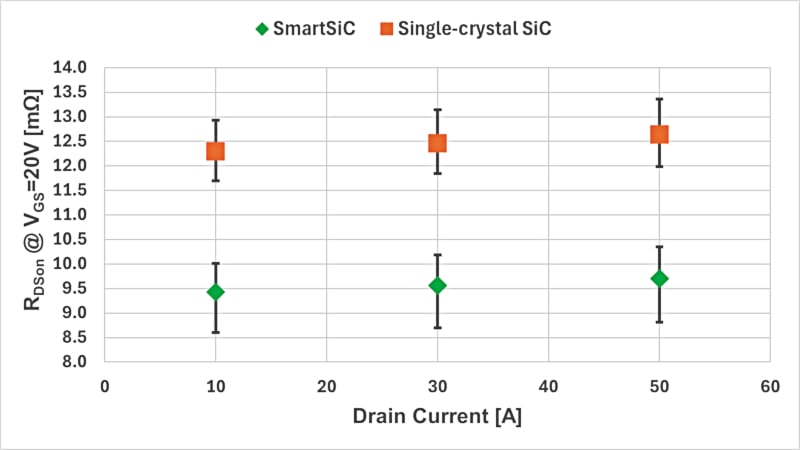

La Figure 3 présente une comparaison du RDSon de l’appareil. Les résultats montrent une réduction moyenne de la résistance à l’état « on » d’environ 24 % en faveur des substrats SmartSiC. Cette amélioration est due à la résistivité beaucoup plus faible de la tranche de support en poly-SiC des substrats SmartSiC, ainsi qu’à sa capacité à former des contacts métalliques à très faible résistivité (contact de drain arrière dans ce cas).

Une telle réduction significative de RDSon (~24%) est proche de ce que l’on peut attendre lors de la transition d’une génération de dispositifs à la suivante.

Figure 3. Comparaison de Ron pour un MOSFET SiC Gen2 de 13 mOhm/650 V fabriqué en SiC monocristallin et en substrats SmartSiC. Image utilisée avec la permission de Bodo’s Power Systems [PDF]

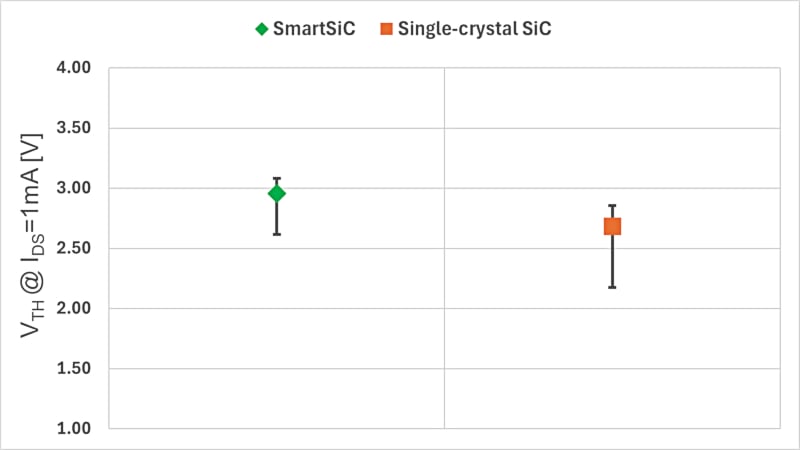

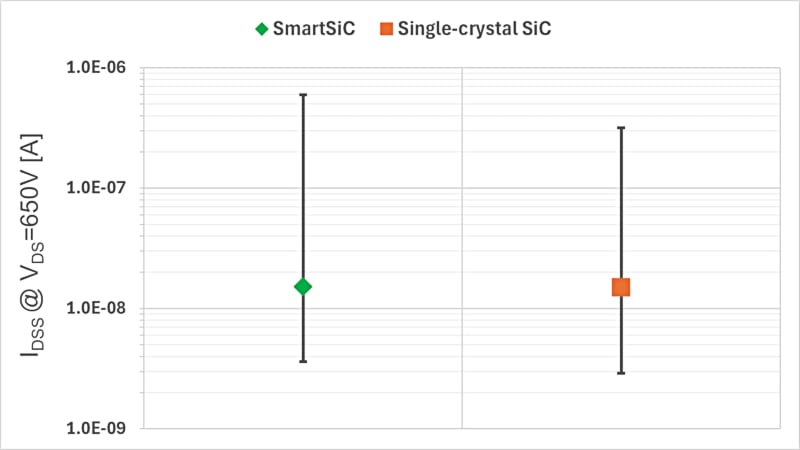

Les Figures 4 et 5 présentent la tension de seuil et le courant de fuite de drain pour le même dispositif fabriqué sur une tranche de SiC monocristallin et un substrat SmartSiC, respectivement. Les résultats montrent un comportement équivalent pour ces paramètres pour les deux types de substrats.

Figure 4. Comparaison de Vth pour un MOSFET SiC Gen2 de 13 mOhm/650 V fabriqué en SiC monocristallin et en substrats SmartSiC. Image utilisée avec la permission de Bodo’s Power Systems [PDF]

Figure 5. Comparaison de IDSS pour un MOSFET SiC Gen2 de 13 mOhm/650 V fabriqué en SiC monocristallin et en substrats SmartSiC™. Image utilisée avec la permission de Bodo’s Power Systems [PDF]

Potentiel pour d’autres dispositifs

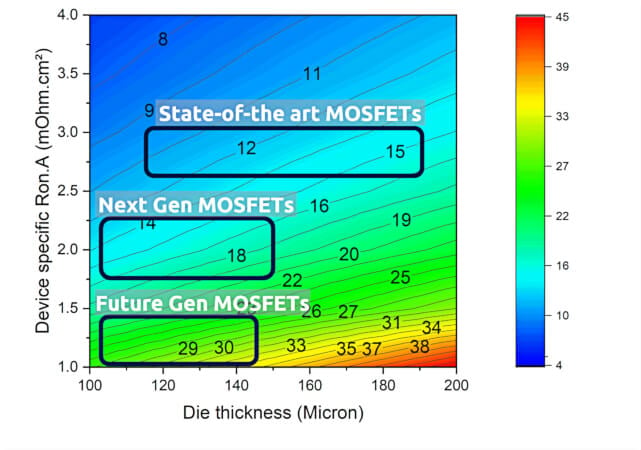

Comme montré dans les sections précédentes, contrairement aux substrats habituels en SiC monocristallin avec une résistivité électrique d’environ 20 mOhm.cm, le matériau SiC polycristallin peut atteindre des niveaux de résistivité aussi bas que 1 mOhm.cm, avec une valeur typique autour de 2 mOhm.cm. De plus, le niveau de dopage élevé du SiC polycristallin contribue à réduire la résistance de contact bien en dessous de 10 µOhm.cm². Ces caractéristiques permettent aux substrats SmartSiC d’augmenter la densité de courant des dispositifs, permettant ainsi de réduire la taille des dispositifs pour les MOSFETs et les diodes.

En particulier, pour les FETs, bien que le gain total dépende de la résistance spécifique initiale du dispositif (Ron.A) et de l’épaisseur de la tranche, la Figure 6 montre que plus la technologie FET est avancée, plus le gain obtenu est élevé. Par Ron.A initial, nous entendons celui du dispositif lorsqu’il est fabriqué sur une tranche de SiC monocristallin. Par exemple, pour un FET avec un Ron.A initial de 2,8 mOhm.cm² et une épaisseur de tranche de 180µm, la figure 5 montre que lorsqu’il est fabriqué sur des substrats SmartSiC, le nouveau Ron.A est de 15 % inférieur (un gain de 15 %). Remarquez que ce gain est indépendant de la tension nominale du dispositif.

La valeur de 2,8 mOhm.cm² prise dans le paragraphe précédent correspond à l’état actuel de l’art pour un MOSFET SiC de 1200 V. Cependant, en regardant les générations de dispositifs à venir dans les prochaines années, des gains (réductions) de Ron.A supérieurs à 20 % peuvent être attendus, présentant toujours l’avantage d’au moins une génération supplémentaire lors de l’utilisation de substrats SmartSiC.

Un cas de gain extrême se produit aujourd’hui avec les JFETs de pointe, le choix privilégié pour les disjoncteurs à semi-conducteurs de 400 V et 800 V pour les véhicules électriques. En prenant comme exemple un JFET SiC de 750 V avec un Ron.A initial autour de 0,7 mOhm.cm², des gains d’environ 30 % peuvent être attendus.

Figure 6. Réduction de Ron.A permise par SmartSiC utilisé pour les MOSFETs SiC de 1200 V en fonction de l’initial Ron.A et de l’épaisseur de tranche. Image utilisée avec la permission de Bodo’s Power Systems [PDF]

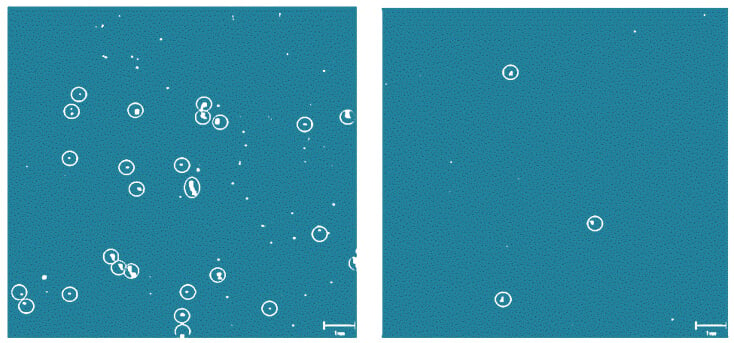

Dernier point mais non le moindre, les substrats SmartSiC montrent, à première analyse, à confirmer par des évaluations électriques spécifiques, une robustesse précieuse contre la dégradation bipolaire. Ce phénomène de dégradation apparaît sur les substrats en SiC en raison du glissement (extension) des dislocations des plans basaux (BPD) dans le cristal de SiC lorsqu’il est exposé à des niveaux élevés de courant bipolaire (en raison des électrons et des trous simultanés). Cela se produit généralement lors de la conduction inverse des MOSFETs en SiC lorsque le courant passe par la diode corporelle de type PiN du transistor.

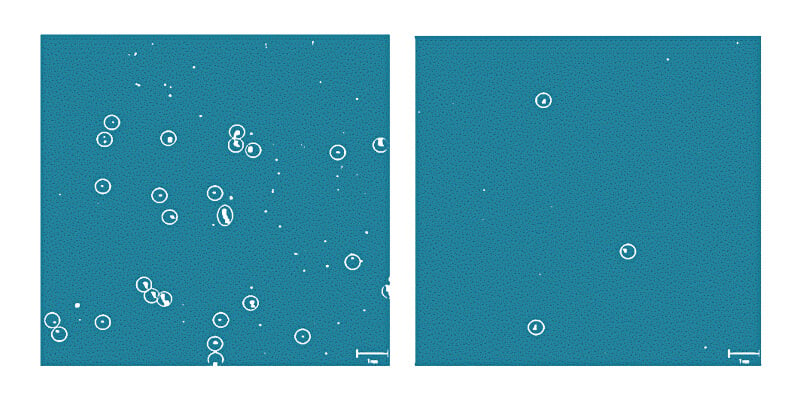

Pour valider cette robustesse, des tranches épitaxiées en SiC monocristallin standard, ainsi que des substrats SmartSiC, ont été soumis à des conditions de stress visant à révéler la dégradation bipolaire. Cela a été réalisé en utilisant la technique E-V-C développée par ITES, Co. Après le stress, il apparaît que tant le nombre de défauts d’empilement de Shockley, l’indicateur que la dégradation bipolaire a lieu, que leur taille typique sont plus faibles dans le cas des SmartSiC comparés aux résultats obtenus dans les tranches de SiC standard. Les résultats suggèrent que la conception SmartSiC possède un avantage inhérent en termes de robustesse contre la dégradation bipolaire par rapport aux tranches monocristallines. Cette caractéristique a été précédemment évaluée par un test de stress de courant direct mené sur une couche épitaxiée de 4H-SiC soumise à une irradiation protonique.

Générations Futures

Dans le contexte actuel d’accélération du déploiement des dispositifs SiC pour la décarbonation de la mobilité et de l’industrie de conversion d’énergie, SmartSiC offre des caractéristiques inégalées, permettant une densité de puissance plus élevée et des applications plus fiables.

Figure 7. Champs d’observation typiques de 10×10 mm après illumination UV (ici 150 W) 420 nm BPF PL de la sévérité de la dégradation bipolaire entre bulk+epi (à gauche) vs. SmartSiC+epi (à droite). Image utilisée avec la permission de Bodo’s Power Systems [PDF]

Les résultats obtenus à partir des MOSFETs fabriqués sur des tranches