Les hautes fréquences de commutation des convertisseurs à composants GaN et SiC posent un défi pour les simulateurs en temps réel utilisés pour les tests hardware-in-the-loop des systèmes de contrôle.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat de contenu numérique exclusif avec Bodo’s Power Systems.

Lorsque la fréquence de commutation des semiconducteurs de puissance dépasse 100 kHz, il n’est pas suffisant de réduire le pas de simulation à juste en dessous d’une microseconde. De plus, les signaux de grille doivent être échantillonnés et moyennés sur un pas de simulation. Cette approche fonctionne bien sur les simulateurs basés sur les processeurs CPU et FPGA pour les onduleurs à commutation dure en mode de conduction continue. Cependant, elle devient imprécise pour les convertisseurs résonants ou les ponts actifs doubles, où les courants changent fréquemment de direction ou entrent en mode de conduction discontinue. Des pas de simulation très petits de quelques nanosecondes sont nécessaires pour simuler de manière précise de telles topologies de convertisseur, ce qui ne peut être réalisé qu’avec des algorithmes spéciaux sur un FPGA.

La simulation de circuits électriques permet aux ingénieurs concepteurs de prédire et d’analyser le comportement d’un dispositif ou d’un système électrique avant la construction d’un prototype. La simulation permet aux ingénieurs de créer un modèle ou un prototype virtuel du dispositif et d’effectuer des tests dans des conditions de fonctionnement normales et défectueuses. Étant donné que des modifications peuvent être apportées rapidement au modèle, la simulation accélère le processus de développement et réduit le délai de mise sur le marché des nouveaux produits. La simulation est utile dans la phase de conception précoce et pour tester le bon fonctionnement d’un dispositif existant qui fera partie d’un système plus vaste. En électronique de puissance, les simulateurs numériques en temps réel sont de plus en plus utilisés pour tester et valider l’équipement de contrôle sans que le circuit de puissance réel soit disponible. Le circuit de puissance réel, qui représente le système commandé, est remplacé par un modèle dynamique approprié calculé sur le simulateur. Étant donné que l’équipement de contrôle est incorporé dans un matériel électronique, cette utilisation est appelée test matériels en temps réel (HIL).

Image utilisée avec l’aimable autorisation d’Adobe Stock

Les simulations HIL permettent de tester l’équipement de contrôle matérielle et logicielle dans un environnement sécurisé. Lors de la simulation en temps réel de l’électronique de puissance, les petites constantes de temps et les dynamiques rapides du circuit électrique posent des défis. Pour que l’équipement de contrôle en cours de test fonctionne comme s’il était connecté à un véritable circuit de puissance, le simulateur en temps réel doit présenter une grande fidélité et un faible retard de bouclage. Cela signifie que les résultats de la simulation doivent représenter avec précision les tensions et courants réels dans le circuit électrique, et qu’ils doivent être calculés et générés en quelques microsecondes après le changement d’un signal à l’entrée du simulateur.

Avec l’avènement des dispositifs à large bande interdite tels que les MOSFET GaN et SiC, les fréquences de commutation des convertisseurs de puissance ont atteint la plage des MHz. Cela pose un défi pour les simulateurs en temps réel, car leur pas de simulation minimum se situe généralement entre 100 ns et quelques microsecondes. Cependant, pour capturer un signal PWM avec une précision suffisante, il doit être échantillonné à une fréquence d’au moins 100 fois la fréquence de commutation. Dans le cas d’une fréquence de commutation de 1 MHz, cela se traduit par un intervalle d’échantillonnage de 10 ns ou moins.

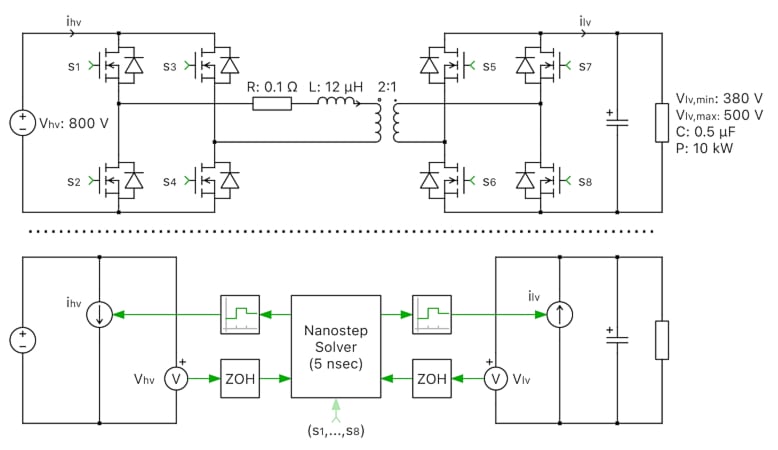

Deux techniques qui facilitent les simulations en temps réel avec de tels petits intervalles d’échantillonnage sont la moyenne sub-cyclique et Nanostep. Alors que la moyenne sub-cyclique peut être appliquée à une large classe d’onduleurs fonctionnant principalement en mode de conduction continue (CCM), un solveur Nanostep est parfaitement adapté à la simulation de topologies de convertisseurs CC/CC résonnants à haute fréquence tels que le pont actif double (DAB) et le LLC.

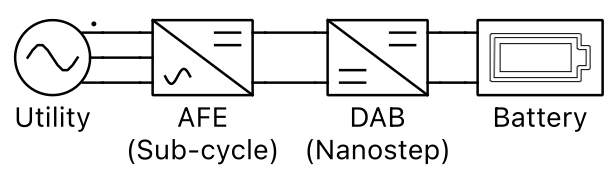

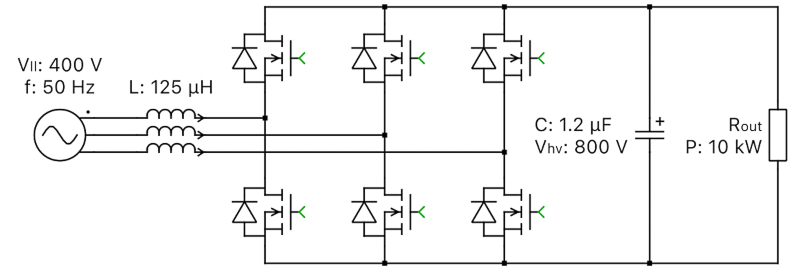

Les architectures courantes d’alimentation électrique combinent un convertisseur AC/DC et un convertisseur DC/DC haute fréquence. Un exemple typique est un chargeur de véhicule électrique composé d’une interface frontale active triphasée (AFE) et d’un DAB, comme le montre la Figure 1. Dans ce chargeur de 10 kW basé sur la technologie de large bande interdite, l’AFE fonctionne en CCM à 140 kHz tandis que le DAB commute à 500 kHz.

Avec les prochaines mises à niveau du micrologiciel pour le RT Box 2 et 3, un circuit de chargeur de ce type peut être simulé sur le FPGA intégré au RT Box. L’AFE peut être simulée avec une moyenne sub-cyclique, tandis que le DAB nécessitera un solveur Nanostep dédié. Cette combinaison de techniques de résolution permet des simulations en temps réel très précises de convertisseurs de puissance avec de hautes fréquences de commutation.

Figure 1. Schéma du système pour un chargeur de véhicule électrique avec une interface frontale active (AFE) et un pont actif double (DAB). Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Moyenne Sub-cyclique

Dans les applications d’électronique de puissance, de nombreux systèmes onduleur-convertisseur, tels que les convertisseurs buck, les convertisseurs boost, les redresseurs à diodes et les onduleurs source de tension (VSI), peuvent être réalisés avec un ou plusieurs demi-ponts. Ces demi-ponts sont constitués de semiconducteurs de puissance montés en série, dont chacun peut être des dispositifs de commutation naturelle (par exemple, des diodes), des dispositifs de commutation forcée (par exemple, des IGBT) ou une combinaison des deux.

Dans la plupart des applications, les demi-ponts sont connectés à un condensateur ou une source de tension côté courant continu. En fonctionnement normal, on peut supposer que la tension continue vdc est polarisée positivement, car sinon, les diodes court-circuiteraient le lien continu. Pendant le fonctionnement, le terminal de phase passe à la tension du lien continu positive ou négative ou reste non connecté.

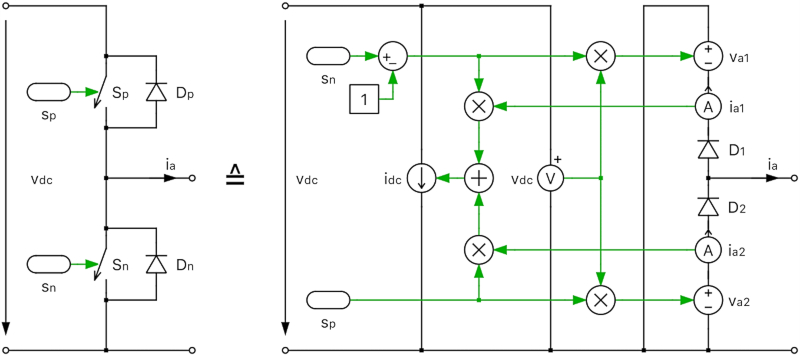

Pour la moyenne sub-cyclique, de tels demi-ponts sont modélisés par une combinaison de deux diodes montées en série et de plusieurs sources de courant et de tension contrôlées pour augmenter la fidélité des simulations en temps réel. Cette approche de modélisation est illustrée dans la Figure 2 pour un demi-pont VSI. Les sources de tension va1 et va2 sont contrôlées par les signaux de commutation sp et sn. Elles appliquent la tension continue vdc côté phase. De même, la source de courant idc est contrôlée par les mêmes signaux de commutation appliquant le courant de phase ia1 ou ia2 côté courant continu.

Les deux diodes sont nécessaires pour simuler la commutation naturelle et le mode de conduction discontinue (DCM). Selon la direction du courant de phase, la diode inférieure ou supérieure conduira, ce qui applique la tension de phase et la tension continue correspondantes. Si aucune des diodes ne conduit, le demi-pont est en DCM, ce qui signifie qu’il est nul.

Figure 2. Modèle de moyenne sub-cyclique pour un demi-pont VSI. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

L’avantage clé de la moyenne sub-cyclique est que les signaux de commutation peuvent non seulement être des signaux binaires représentant l’état de marche (s = 1) et l’état d’arrêt (s = 0) du dispositif, mais aussi des valeurs moyennes à court terme (0 ≤ s ≤ 1) représentant la durée relative de fonctionnement ou le rapport cyclique du dispositif pendant une étape de simulation. Ces valeurs moyennes peuvent être obtenues en échantillonnant les signaux PWM à chaque cycle d’horloge FPGA, généralement inférieur à 10 ns. Même avec des fréquences de commutation élevées et des pas de simulation de deux ordres de grandeur supérieurs au cycle d’horloge FPGA, le courant de phase obtenu est essentiellement précis car les volt-secondes des signaux moyens correspondent aux volt-secondes des signaux PWM d’origine. Cependant, toutes les harmoniques de commutation ne peuvent pas être conservées avec de grands pas de simulation. Si la taille du pas est trop grande, les tensions et courants calculés peuvent présenter une erreur grossière.

Le principal inconvénient de la moyenne sub-cyclique réside dans l’imprécision causée par le passage nul du courant de phase. Comme la direction du courant de phase n’est déterminée qu’une fois par étape de simulation, des volt-secondes légèrement incorrectes peuvent être appliquées pendant l’étape où le courant a traversé zéro ou est entré en DCM. Alors que cette imprécision est acceptable pour les onduleurs fonctionnant en CCM et sans changements fréquents de direction du courant, tels que les onduleurs connectés au réseau, ce n’est peut-être pas le cas pour d’autres convertisseurs, en particulier les convertisseurs à commutation naturelle, fonctionnant à des fréquences de commutation élevées.

La Figure 3 représente le circuit AFE triphasé de l’exemple de chargeur de véhicule électrique. L’AFE avec des MOSFET SiC commutant à 140 kHz est le modèle de référence pour valider la technique de moyenne sub-cyclique. Dans ce modèle de circuit, la charge de l’étage DAB est représentée par une résistance équivalente Rout.

Figure 3. Circuit AFE avec des MOSFET SiC. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

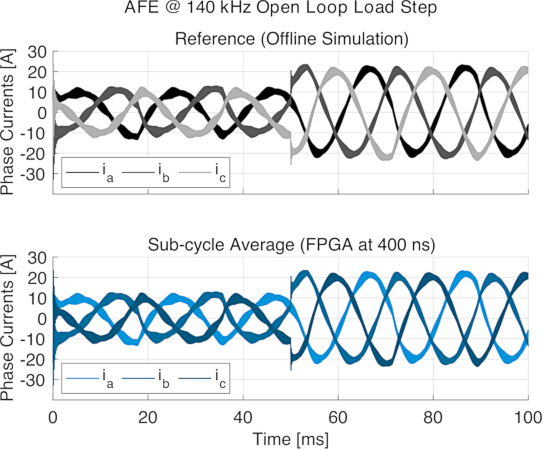

La Figure 4 montre les courants d’entrée de l’AFE lors d’un changement d’étape de demi-charge à charge maximale. Les simulations hors ligne ont généré les résultats de référence dans PLECS avec un solveur à pas variable et des interrupteurs idéaux. Ils sont comparés aux formes d’onde obtenues à partir des simulations en temps réel avec le RT Box. L’étape de modèle de 400 ns correspond à la taille de l’étape qui peut être atteinte sur un RT Box 2 ou 3 en utilisant le nouveau solveur de circuit basé sur le FPGA avec une moyenne sub-cyclique. Les signaux de commande des MOSFET sont générés par un contrôleur à boucle ouverte afin de permettre une comparaison directe entre les deux approches de modélisation différentes.

Figure 4. Simulation hors ligne avec PLECS comparée à la simulation en temps réel sur le RT Box. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

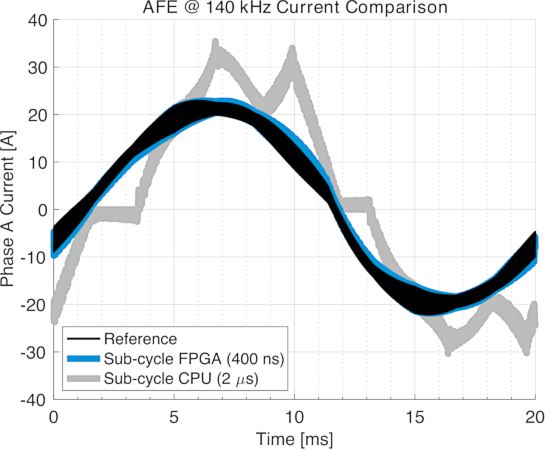

La comparaison des courants de phase démontre la précision du modèle de moyenne sub-cyclique. La Figure 5 montre l’AC en phase A pour un seul cycle de la fréquence du réseau. La simulation basée sur un FPGA avec une étape de 400 ns correspond étroitement à la forme d’onde de référence. Cependant, l’approche de moyenne sub-cyclique nécessite une petite taille de pas de modèle pour une solution précise. Avec une taille de pas de 2 μs, qui représente le calcul du modèle de moyenne sub-cyclique sur un processeur CPU du RT Box, les formes d’onde de courant présentent une grande erreur.

Cette erreur est causée par la détection retardée des changements de direction du courant, qui peut se produire lorsque les impulsions PWM sont plus courtes que la taille de pas de simulation. Dans le modèle de la Figure 2, les valeurs crête des tensions moyennes va1 et va2 peuvent ne pas être assez grandes pour faire commuter directement le courant de phase d’une diode (D1 et D2) à l’autre. Au lieu de cela, les deux diodes peuvent s’ouvrir et bloquer le courant à zéro. Cet effet peut être observé dans la Figure 5, où avec une taille de pas de 2 μs, le courant de phase A est déformé autour des traversées de zéro. Le même comportement dans les phases B et C se manifeste par des distorsions près du pic de la forme d’onde de phase A via un décalage de la tension neutre.

Figure 5. Forme d’onde du courant de phase A sur un cycle de ligne. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

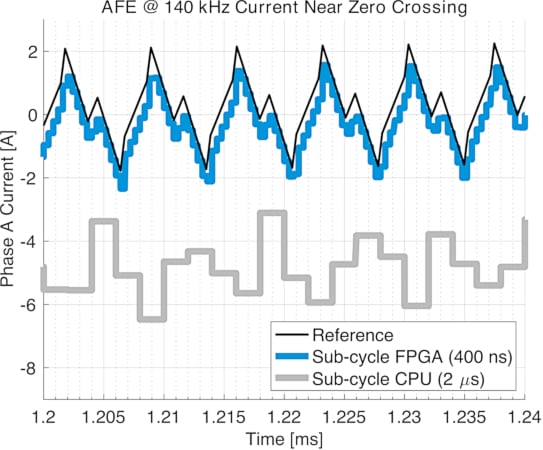

La Figure 6 illustre en détail comment la direction du courant de phase change de négative à positive. Malgré les traversées zéro répétitives, la simulation basée sur le FPGA s’écarte légèrement de la référence. Avec la taille de pas de 400 ns, le solveur s’exécute près de 18 fois dans un cycle de commutation, de sorte que les valeurs de tensions moyennes sont souvent proches des tensions instantanées. La commutation ponctuelle occasionnelle du courant à zéro, causée par des diodes ouvertes, est transitoire et n’a qu’un impact mineur sur les résultats. En revanche, si les tensions sont moyennées sur une étape de modèle CPU de 2 μs, elles échouent à commuter le courant.

Figure 6. Vue détaillée de la forme d’onde du courant de phase A. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Nanostep

L’approche de moyenne sub-cyclique devient imprécise pour les convertisseurs électroniques de puissance où la direction du courant de phase change fréquemment. C’est particulièrement vrai pour les convertisseurs DC/DC avec un lien AC inductif, où le transfert de puissance est très sensible au déphasage entre le courant et les signaux PWM. Une détection retardée des traversées nulles de l’AC peut entraîner des erreurs considérables. Cela est dû au fait que les courants positifs, négatifs et nuls correspondent à une topologie de circuit différente régie par un autre ensemble d’équations différentielles.

Pour détecter les traversées zéro aussi rapidement que possible, Plexim a développé le solveur Nanostep qui sera disponible pour le RT Box plus tard cette année. Dans une simulation Nanostep, les valeurs des courants de l’inducteur et des tensions des condensateurs résonants sont mises à jour à chaque cycle d’horloge FPGA. Comme le calcul d’une nouvelle valeur nécessite un pipeline d’opérations arithmétiques et prend plusieurs cycles d’horloge, les valeurs de toutes les topologies possibles sont calculées en parallèle. La validité d’une topologie dépend des signaux de grille les plus récents et de la dernière direction du courant de l’inducteur. Un courant d’inducteur qui change de direction ou est bloqué à zéro représente une condition limite qui limite la plage de validité de certaines topologies. La décision sur quelle topologie doit être appliquée n’est prise qu’après que toutes les valeurs ont été calculées et est basée sur les conditions limites.

La Figure 7 montre un modèle Nanostep de l’étage DAB du chargeur de véhicule électrique. La fréquence de commutation du convertisseur est de 500 kHz, et le temps mort est de 120 ns. Un déphasage entre la modulation des interrupteurs primaires et secondaires contrôle le transfert de puissance.

Le solveur Nanostep intègre le réseau de commutation du convertisseur et les éléments de stockage d’énergie. L’échantillonnage des signaux de grille, l’intégration du courant de l’inducteur et la détection des traversées zéro du courant se produisent au cycle d’horloge FPGA de 5 nanosecondes ou moins. Avec un taux d’échantillonnage de 5 ns, le solveur Nanostep peut détecter des déphasages aussi bas que 0,5% pour une fréquence de commutation de 500 kHz.

Figure 7. Modèle Nanostep pour un pont actif double s’interfaçant avec un circuit externe. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Les dynamiques du circuit externe d’intérêt, à savoir les tensions des condensateurs d’entrée et de sortie vHV et vLV, sont généralement beaucoup plus lentes que les dynamiques du réseau de commutation interne. Le circuit externe est simulé à l’aide d’un solveur générique implanté sur le FPGA ou le CPU avec une pas de modèle beaucoup plus grand. Les valeurs typiques de pas varient de quelques centaines de nanosecondes à quelques microsecondes. Dans cette application, la pas de modèle de 400 ns de l’AFE est utilisée comme intervalle de communication avec le solveur Nanostep. Les entrées du solveur Nanostep sont les tensions terminales du convertisseur, échantillonnées au pas de modèle. Le solveur Nanostep moyenne les courants d’entrée et de sortie du convertisseur sur un pas de modèle pour calculer correctement les courants iHV et iLV injectés dans le réseau externe.

Les limites du solveur Nanostep sont dues à l’interface avec le circuit externe qui est résolu à un pas de modèle plus grand. Les tensions aux bornes du convertisseur sont supposées constantes pendant un pas de modèle. Le pas de modèle dicte également la fréquence de mise à jour de la sortie du matériel analogique, ce qui affecte le retard de bouclage. Enfin, les conditions de panne internes ne sont pas simulées mais peuvent être détectées lorsque tous les signaux de grille dans l’intervalle d’échantillonnage de 5 ns entraîneraient un court-circuit des bornes CC du convertisseur.

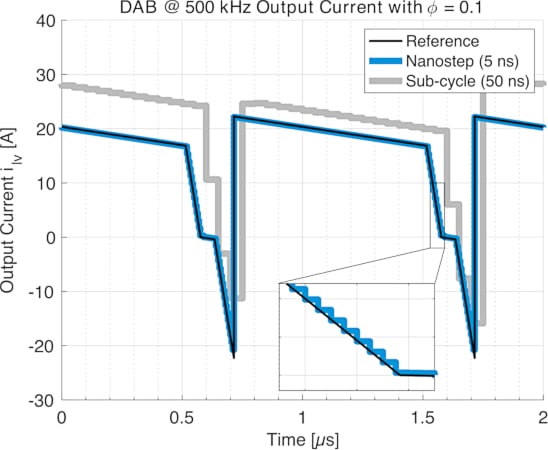

La Figure 8 évalue la précision du solveur Nanostep par rapport à des simulations hors ligne avec des interrupteurs idéaux dans PLECS et à un modèle hypothétique de moyenne sub-cyclique avec une taille de pas de 50 ns. Le modèle de 50 ns ne peut pas être réalisé sur le RT Box. Le convertisseur fonctionne avec un déphasage constant de 0,1Tsw ou 200 ns. Avec la plus grande taille de pas, la moyenne des signaux de grille sur l’intervalle de 50 ns conduit à une erreur dans le courant de sortie. Les traversées zéro du courant pendant l’intervalle de temps mort sont également manquées. En comparant le courant moyen sur un modèle de pas, le solveur Nanostep et la solution de référence sont précis à moins de 1%, tandis que le modèle avec une taille de pas de 50 ns présente une erreur de 40%.

Figure 8. Le courant de sortie du DAB a été simulé avec une taille de pas de 5 ns et 50 ns. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

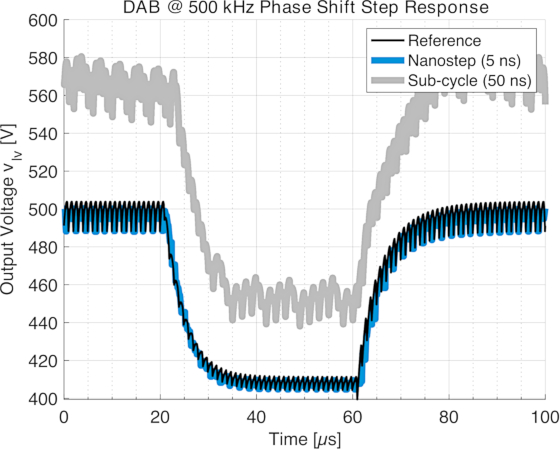

En utilisant les valeurs moyennes des calculs du solveur Nanostep de 5 ns comme interface vers le circuit externe, les grandes dynamiques des ports d’entrée et de sortie du convertisseur sont conservées. La Figure 9 montre la réponse du modèle à un changement d’étape dans le déphasage du modulateur avec une charge résistive constante. Le convertisseur démarre à une tension de sortie de 500 V à une puissance nominale, passe à un niveau de puissance inférieur en raison d’une diminution du déphasage, puis revient à la phase initiale. Les dynamiques de tension du solveur Nanostep, combinées à une taille de pas de 400 ns, correspondent étroitement à la solution de référence. Le déphasage supplémentaire est dû à la moyenne du courant par le solveur Nanostep et à la durée de l’étape de modèle. Le modèle de moyenne sub-cyclique n’est pas utilisable car il délivre une puissance excessive, et la tension de sortie, par conséquent, n’atteint jamais la tension de sortie en régime permanent attendue.

Figure 9. Réponse du DAB de 500 kHz à un changement d’étape dans le déphasage du modulateur. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems [PDF]

Simulation en temps réel

La simulation en temps réel peut tester et valider l’équipement de contrôle, même pour les convertisseurs de puissance de nouvelle génération basés sur SiC et GaN. En raison des hautes fréquences de commutation et des courtes constantes de temps des convertisseurs avec des dispositifs à large bande interdite, les simulateurs en temps réel doivent capturer les signaux de commande de grille avec des intervalles d’échantillonnage de quelques nanosecondes et utiliser des techniques numériques spéciales pour détecter les traversées zéro du courant avec une grande précision dans le temps.

Plexim a développé de puissants algorithmes pour répondre à ces exigences : La moyenne sub-cyclique est une méthode polyvalente pour simuler les onduleurs source de tension fonctionnant principalement en CCM. De plus, le nouveau solveur Nanostep permet la simulation en temps réel de convertisseurs CC/CC résonnants et haute fréquence fonctionnant bien au-dessus de 100 kHz. Le solveur Nanostep détecte les changements de direction du courant avec une résolution de 5 ns, ce qui le rend parfait pour les topologies sélectionnées où le courant change fréquemment de direction ou entre en DCM.

Les mises à niveau du micrologiciel gratuites, qui seront publiées en 2024, permettront aux RT Box 2 et 3 de simuler des modèles de moyenne sub-cyclique et Nanostep sur le FPGA intégré. Des simulations de référence d’un AFE triphasé à 140 kHz et d’un DAB à 500 kHz montrent que ces techniques de simulation en temps réel produisent des résultats très précis.

Cet article est initialement paru dans le magazine Bodo’s Power Systems [PDF].