Les améliorations dans la taille et la fabrication des wafers en carbure de silicium (SiC) permettent de produire des semi-conducteurs de puissance abordables et à haute efficacité.

Cet article est publié par pÉlectrique dans le cadre d’un partenariat exclusif de contenu numérique avec Bodo’s Power Systems.

Des énergies renouvelables à la mobilité électrique, les semi-conducteurs de puissance en carbure de silicium (SiC) sont essentiels pour poursuivre la durabilité par l’électrification. Bien que cette technologie offre un avantage de rendement précieux par rapport aux alternatives en silicium, les composants SiC restent relativement coûteux en raison des défis de fabrication. Surmonter ces défis est la clé pour produire des composants commercialement viables.

Croissance des cristaux de SiC

Le carbure de silicium possède une structure cristalline complexe avec de nombreux polytypes différents. Il présente une dureté extrême — deux propriétés peu adaptées à la fabrication de composants électroniques de précision avec des tailles de caractéristiques sub-micrométriques. Alors que les lingots de silicium pour la production de wafers peuvent être produits de manière régulière avec des résultats presque parfaits, un lingot ou boule de SiC contient typiquement plusieurs types de défauts résultant d’une croissance imparfaite.

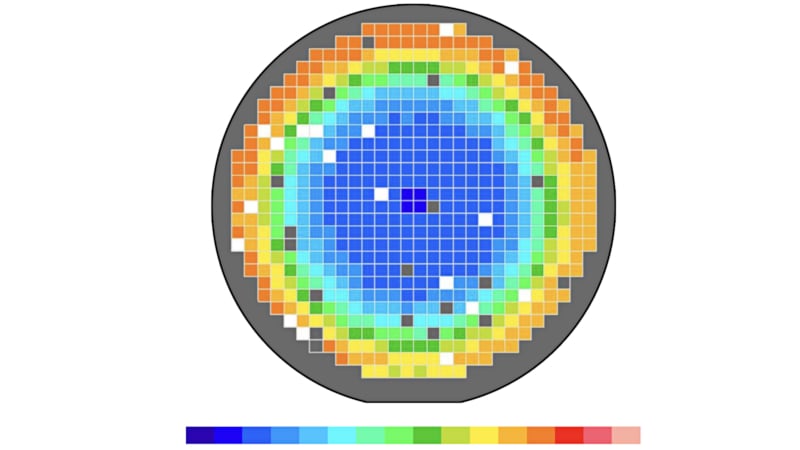

La Figure 1 montre les résultats d’une analyse des sites défectueux sur un wafer de qualité adéquate pour la production de diodes à haut rendement.

Figure 1. Analyse des sites défectueux sur un wafer en SiC. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems []

Parmi les défauts les plus graves, les dislocations de plan basal (BPD) causées par le désalignement des atomes peuvent introduire des contraintes qui affectent l’intégrité globale du réseau cristallin. D’autre part, des défauts tels que les dislocations à vis (SD) se forment autour d’un axe et peuvent produire des défauts visibles à la surface après l’épitaxie. Améliorer le contrôle des conditions de croissance des cristaux, ainsi que l’application de traitements post-croissance, peut aider à atténuer les SD.

Les défauts en forme de carotte, des inclusions coniques ou en forme de carotte dans le cristal de SiC, se produisent lorsque les dislocations à vis intersectent la surface du cristal pendant la croissance, créant un canal pour l’incorporation d’impuretés dans le cristal, causant des inclusions en forme de carotte. Il peut également y avoir des dislocations à cœur creux, appelées micropipes. D’autres causes potentielles de défauts incluent un empilement irrégulier des cristaux, des atomes manquants, des atomes supplémentaires, et des joints de grains qui peuvent s’étendre à travers le réseau cristallin.

Défis de taille et d’épitaxie

Après la croissance de la boule, les wafers sont découpés par sciage avec des scies à fil de diamant, puis polis. Ces processus sont longs et coûteux en raison de l’extrême dureté du SiC, mais certains défauts restent inévitablement dans et sous la surface du substrat. Lorsque l’épitaxie est appliquée, ces imperfections peuvent entraver la croissance des couches, entraînant un regroupement des étapes, ralentissant effectivement la formation des étapes et provoquant des interférences et des variations indésirables de la hauteur des étapes. Les imperfections sous la surface cristalline affectent les paramètres du dispositif tels que les caractéristiques de la diode de corps et la qualité de l’interface avec l’oxyde de grille.

De plus, la planéité des sites locaux est beaucoup plus difficile à atteindre après le broyage et le polissage que pour le silicium ordinaire. Cependant, une surface plane est essentielle pour la fabrication des dispositifs afin de permettre le bon focalisation des équipements de lithographie et ainsi atteindre des dimensions précises des dispositifs, affectant directement les paramètres électriques.

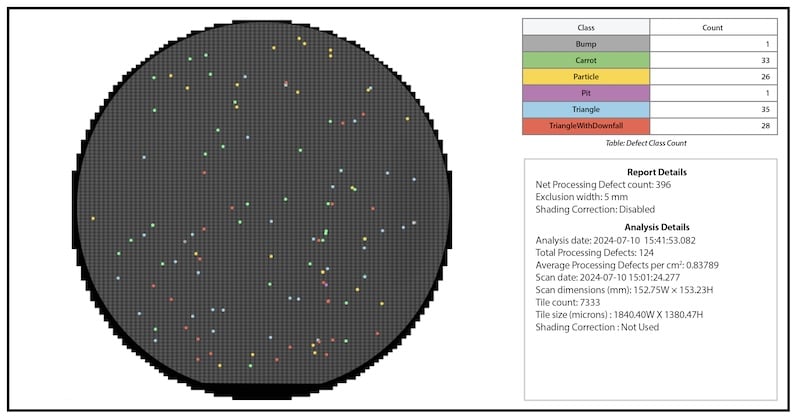

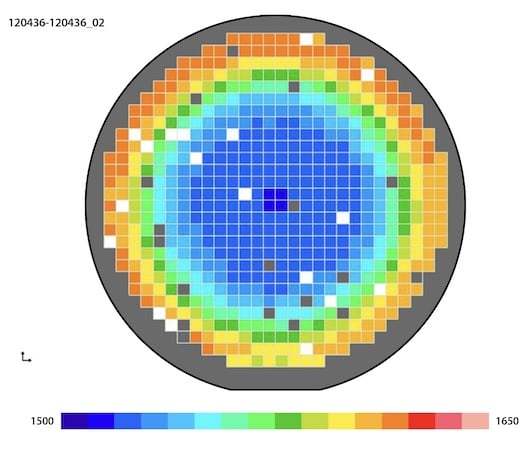

Le scanneur essaie de se concentrer sur le centre de chaque site. Comme la profondeur de champ de l’équipement lithographique est relativement faible, la variation de forme du wafer signifie que l’image peut être moins nettement mise au point à certains endroits. Par la suite, le réacteur cause des variations dans le dopage épitaxial et l’épaisseur, entraînant une dispersion des paramètres des dispositifs. La tension de claquage (BVDSS) des MOSFETs en SiC est connue pour être particulièrement affectée (Figure 2). Des défauts sévères à certains sites sur un wafer donné peuvent produire des puces qui ne fonctionnent pas du tout.

Figure 2. BVDSS mesuré des MOSFETs fabriqués à différents sites de la surface du wafer, montrant une variation radiale due au dopage épitaxial et à l’épaisseur. Image utilisée avec l’aimable autorisation de Bodo’s Power Systems []

Définir la qualité des wafers

L’étendue des imperfections dans un wafer affecte significativement le nombre de bonnes puces que le wafer produira. Plus il y a d’imperfections, plus le rendement est faible, ce qui augmente le prix par unité du composant. D’un autre côté, établir une specification élevée peut faire grimper le prix des wafers nus.

Lors de l’organisation de l’approvisionnement en epiwafers en SiC, les fabricants de puces doivent spécifier le niveau acceptable d’imperfections. L’industrie a dû apprendre à établir des spécifications réalisables, permettant aux fournisseurs de livrer une qualité adéquate de manière économique tout en permettant aux fabricants de dispositifs de produire suffisamment de puces fonctionnelles pour rester commercialement viables.

Les fournisseurs d’epiwafers fournissent un certificat d’analyse (CofA) qui confirme la conformité à la spécification convenue. À mesure que la compréhension des problèmes a progressé, les fabricants de dispositifs ont demandé aux fournisseurs d’epiwafers de fournir plus d’informations dans le CofA.

Au début de l’histoire du SiC, les fournisseurs et les fabricants de dispositifs se concentraient uniquement sur quelques paramètres de wafer. Historiquement, par exemple, seul le nombre total de défauts à la surface du wafer était surveillé. Il est désormais courant que le CofA spécifie le pourcentage de sites qui doivent être sans défaut, avec des limites spécifiques sur les défauts de préoccupation sérieuse, tels que les BPD. Le pourcentage de sites présentant zéro défaut BPD est le plus important dans les wafers destinés à la production de MOSFETs.

La planéité de la surface était également généralement indiquée pour l’ensemble du wafer. L’expérience a montré que les fabricants de dispositifs ont besoin d’assurances concernant la planéité dans des zones plus localisées sur la surface du wafer. En conséquence, la planéité des sites locaux est devenue un paramètre généralement demandé.

La Figure 3 montre un échantillon de paramètres d’un CofA typique d’epiwafers en SiC. Dans cette liste, la planéité locale des sites est exprimée comme le SBIR, ou (S)ite (B)ackside (I)deal Focal Plane (R)ange. En considérant la topologie de surface comme un ensemble de pics et de creux au-dessus et en dessous du point central du site, le SBIR est la somme de la hauteur du pic le plus élevé et de la profondeur du creux le plus bas. Bien qu’une valeur SBIR de 2µm ait été jugée adéquate, 1.2µm est une plage plus acceptable pour minimiser l’écart de planéité comme cause de défauts dans les dispositifs fabriqués.

Processus et équipements

La connaissance croissante des types de défauts dans les epiwafers, de leurs causes et de leurs effets sur la qualité et les performances des composants a entraîné des améliorations dans les processus et l’équipement disponibles pour la production de wafers.

Tableau 1. Paramètres clés spécifiés dans le CofA.

Caractéristiques de la couche épitaxiale | ||

Épaisseur de la couche Epi-Layer1 (tampon) | 1 | μm |

Concentration de dopage de la couche Epi-Layer1 (tampon) | 1.00 E18 | At/cm3 |

Épaisseur de la couche Epi-Layer2 (dérive) | 14.5 | μm |

Concentration de dopage de la couche Epi-Layer2 | 6.0 E15 | At/cm3 |

Caractéristiques post-épitaxie | ||

Déformation, epi-wafer | ≤ 50 | μm |

Courbure, epi-wafer | ± 40 | μm |

Variation de l’épaisseur totale (TTV), epi-wafer | ≤ 10 | μm |

Planéité des sites epi-wafer; SBIR (LTV) MAX | ≤ 5 | μm |

Planéité des sites epi-wafer; SBIR (LTV) | ≤ 2 | μm |

Rugosité de surface | < 0.5 | nm |

Exigences d’inspection visuelle de la surface frontale | ||

Rayures – cumulatif | ≤ 150 | mm |

Densité des défauts de surface | < 0.5 (Typique 0.1) | cm3 |

Zone sans défaut (2 mm□) | > 93 | % |

Densité BPD | < 0.5 (Typique 0.1) | cm3 |

Zone sans BPD (2 mm□) | > 90 | % |

La dureté extrême du SiC pose des défis dès les premières étapes de la fabrication des wafers. Les disques de coupe ou les scies à fil de diamant utilisées pour découper les wafers à partir de la boule présentent un risque élevé de rupture. La découpe au laser permet de produire plus de substrats à partir de la précieuse boule et sera probablement privilégiée dans un avenir proche. De plus, le découpage au laser peut réduire l’espace perdu entre les dies adjacents et augmenter le nombre de dies par wafer.

En outre, des travaux sont en cours pour minimiser ce que l’on appelle l’exclusion des bords et permettre l’application de processus plus près du bord du wafer. Par de meilleures données sur les caractéristiques des matériaux dans les 4-6 mm autour du bord du wafer, il est possible d’augmenter l’utilisation de cette zone pour produire davantage de puces utilisables et diminuer le coût unitaire des dispositifs.

La commercialisation stimule également les améliorations dans la conception des réacteurs. Les réacteurs multi-wafers deviennent plus économiques à mesure que la demande augmente. D’autre part, le traitement d’un seul wafer offre une plus grande flexibilité pour perfectionner le réglage. En outre, les avancées dans le contrôle du mouvement photolithographique permettent des tailles de pas plus petites qui minimisent et réduisent les instances de défauts. La taille de pas typique est maintenant d’environ 25 % de celle des générations précédentes de matériel.

De plus, la profondeur de champ est généralement plus grande, ce qui permet une tolérance accrue pour la planéité de la surface. Les sites avec un SBIR plus élevé peuvent désormais produire des dispositifs dont les paramètres sont dans la plage acceptable. Les améliorations qui optimisent le flux de vapeur de dopant et le mouvement des wafers dans le réacteur minimisent également les différences dans les propriétés des dispositifs produits à différents sites sur le wafer en garantissant un dopage épitaxial et une épaisseur plus uniformes.

De plus, les meilleures pratiques s’adaptent, comme le nettoyage régulier des réacteurs. À mesure que les particules s’accumulent sur les composants internes et les mécanismes du réacteur, leur élimination empêche la chute qui pourrait autrement produire des défauts de formes et de tailles variées à la surface du wafer.

SiC vs. Silicium

Le SiC est un substrat bien plus difficile que le silicium à chaque étape de la fabrication des composants, depuis la production de lingots ou de boules jusqu’à la taille, l’épitaxie, la lithographie et le découpage. Comprendre et surmonter ces défis a défini le parcours de cette technologie depuis la recherche jusqu’à la disponibilité commerciale. Les justifications techniques pour adopter le SiC dans les convertisseurs et les entraînements à haute efficacité sont claires. L’argument économique devient également de plus en plus convaincant avec chaque amélioration des processus de production, de l’équipement et des pratiques.

Cet article est paru à l’origine dans Bodo’s Power Systems [] et est coécrit par Tony Witt, scientifique des dispositifs, et Timothy Han, président de SemiQ.